Initially developed by Apple and implemented by Intel, AMD, Nvidia, ARM and IBM to name a few, OpenCL is an industry standard managed and maintained by the Khronos Group. It is the first open, royalty-free, unified programming model for accelerating algorithms on heterogeneous systems.

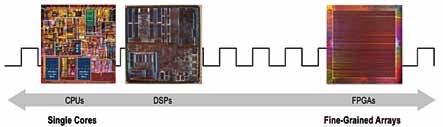

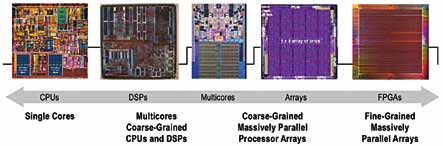

The single-core CPUs that were initially used for computation, were soon replaced with multiple-core CPUs for higher performance. Today, there is a shift to comparatively smaller multi-core systems. Their small size is achieved by placing a general-purpose graphical processing unit (GPU), digital signal processor (DSP) or field-programmable gate array (FPGA) chips next to a CPU. However, engineers face the challenge of accelerating their programs across all of these different types of hardware. To tackle this challenge, they are looking for a single open standard programming model to bridge the hardware gap—and OpenCL could be the answer.

What is OpenCL?

For a software engineer OpenCL is a programming model, whereas for a system architect it is a methodology. OpenCL allows the use of a ‘C’-based language for developing code across different platforms including CPUs, GPUs, DSPs and FPGAs. By utilising the standard ‘C’ language (C99) and OpenCL C (standard ‘C’ with some extensions), it can provide the solution for a single unified design flow in a different manner by using the open standard extension of ‘C’ language.

[stextbox id=”info” caption=”Design challenges to overcome while using FPGAs”]1. Generally, programmers have difficulty using FPGAs as massive multi-core devices to accelerate parallel applications.

2. A programming model is needed that allows the designer to think about the FPGA as a configurable multi-core device.

3. Today, the FPGA’s programming model revolves around RTL (VHDL/Verilog)—state machines, datapaths, arbitration, buffering, etc.

4. It is more difficult to develop an OpenCL program for an FPGA than more natural hardware platforms such as CPUs and GPUs.[/stextbox]

Combining the OpenCL programming model with FPGA architecture provides a powerful solution for system acceleration. OpenCL is a standard multi-core programming model that can be used to provide a higher-level layer of abstraction for FPGAs.