Ideal for applications in industrial, automotive, and consumer electronics, this ready-to-integrate IP core enables fast, reliable data exchange with minimal resource usage and faster time-to-market.

In the fast-evolving landscape of embedded systems and industrial automation, reliable serial communication remains a cornerstone of system design. For design engineers working on FPGA-based platforms, a robust and efficient Universal Asynchronous Receiver/Transmitter (UART) module can significantly streamline communication between microcontrollers, peripherals, and external devices. From consumer electronics to automotive systems, industrial controls, and IoT edge devices, UART interfaces play a critical role in ensuring low-complexity, cost-effective data exchange over short to medium distances.

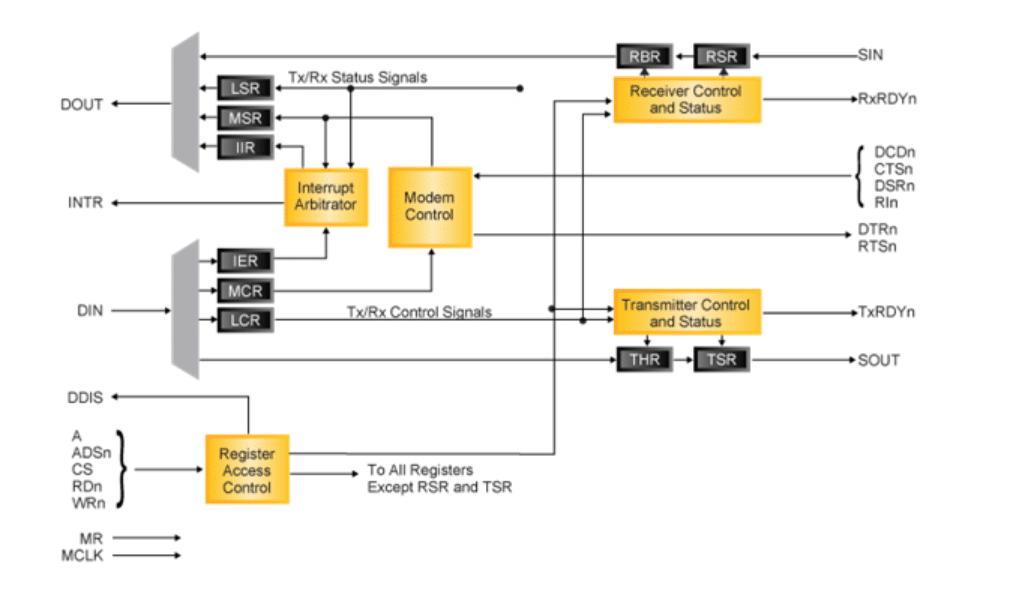

To support rapid development and reduce design complexity, Lattice Semiconductor offers a fully verified UART reference design tailored for its FPGAs, enabling engineers to quickly integrate serial communication in their applications without starting from scratch. Lattice’s UART reference design is a complete solution that provides a high-performance and configurable IP core for serial communication. It facilitates asynchronous, full-duplex communication between digital systems and external peripherals over RS232-like interfaces. The module supports standard UART features such as 8-bit data format, 1 start bit, 1 stop bit, and parity bit support.

Designers can also configure the baud rate dynamically using an input clock and a programmable divisor, offering flexibility across different system requirements.Built for simplicity and efficiency, this reference design includes both transmitter and receiver blocks, FIFO buffers, and optional interrupt support. The integration of transmit and receive FIFOs ensures smooth data handling and reduces the risk of data overrun or loss—particularly useful in systems where processor resources are limited. The interrupt mechanism further allows responsive handling of communication events, improving overall system efficiency.

This UART IP core is optimized for use with Lattice’s low-power FPGA families, including the LatticeXP2™, LatticeECP3, and MachXO/MachXO2 devices. By leveraging the UART reference design, developers can minimize verification cycles and accelerate time-to-market while maintaining a compact silicon footprint and low power profile.To aid faster adoption, the reference design package comes with all essential documentation, including synthesis constraints, testbenches, and simulation support. This makes it easier for design teams to evaluate, modify, and deploy the UART module according to their application needs.

Whether used in system monitoring, debugging, configuration interfaces, or peripheral control, this UART reference design delivers the reliability and ease-of-use that modern electronic systems demand. The design represents a practical and proven solution for embedding serial communication into your next design—offering design engineers both flexibility and confidence in implementation.

Lattice Semiconductor has tested this reference design. It comes with a bill of materials (BOM), schematics, assembly drawing, printed circuit board (PCB) layout, and more. The company’s website has additional data about the reference design. To read more about this reference design, click here.