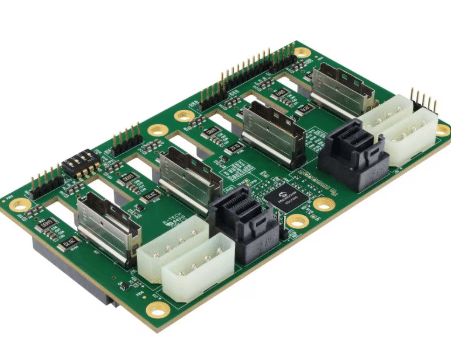

Designed to simplify storage system integration. Supporting SAS, SATA, and NVMe drives, advanced LED control, secure boot with hardware encryption, and multi-backplane configurations — it delivers industry-standard UBM compliance with scalable performance for modern data storage architectures.

The EEC1005-UB2 by Microchip Technology is a versatile and highly configurable Universal Backplane Management (UBM) processor designed to streamline storage enclosure management for hard drive backplanes. This device delivers seamless system integration through industry-standard communication protocols, ensuring efficient monitoring and reporting for computing host systems. The family, distinguished by the UB1 and UB2 suffixes in their ordering numbers, represents an evolution in functionality — with the UB2 variant offering significant enhancements over the original UB1 (formerly labeled as EEC1005). The EEC1005-UB2 offers broad compatibility with SAS, SATA, and NVMe storage devices through support for multiple host interfaces.

Specifically, it allows the use of the SFF-8654 Slimline connector for SAS signal routing, enabling the Host Bus Adapter (HBA) to manage SAS or SATA drives. The same connector, when used with PCIe signal routing, allows the HBA to handle NVMe drives, maintaining UBM protocol compatibility and optionally supporting SGPIO depending on configuration. Additionally, EEC1005-UB2 enables drive connectivity via both U.2 and U.3 drive-facing connectors, further boosting system design flexibility. The device is designed to manage multiple backplanes within a single chassis, supporting scalable storage solutions.

It has advanced storage LED management, which complies with SFF-8489 IBPI specifications by default. It can control two or three LED IBPI blinking patterns for up to 16 drives, and also allows users to define custom blink patterns through FRU programming. The device’s secure boot mechanism ensures system integrity by authenticating and decrypting the Flash boot image using AES-256 encryption, ECDSA P-256 signing, and SHA-256 hashing via its built-in cryptographic hardware accelerators.

It provides secure storage of private keys and IDs through its lockable One-Time Programmable (OTP) memory space. The device further supports NVMe hot-plug and power disable features, as well as flexible host interface configuration via a single analog pin, allowing for seamless switching between SGPIO and UBM protocols as needed. Available in both 84-pin and 144-pin WFBGA package options, the EEC1005-UB2 simplifies integration into diverse system architectures.

Microchip Technology has tested this reference design. It includes a bill of materials (BOM), schematics, assembly drawing, printed circuit board (PCB) layout, and more. Additional data about the reference design is available on the company’s website. To learn more, click here.