New circuits use random bits to solve software problems faster, showing a new way electronics can handle difficult calculations.

Many computational problems, such as optimization and integer factorization, remain challenging for traditional computers. These problems often require exploring a large number of possible solutions, which makes them slow and inefficient to solve sequentially. Probabilistic Ising machines (PIMs) are computing systems designed to address these challenges using networks of probabilistic bits (p-bits). P-bits switch between 0 and 1 but can be guided to converge toward desired solutions, allowing the system to explore the solution space more efficiently than conventional approaches.

A major obstacle in building PIMs is generating random bit sequences, which are central to probabilistic computation. CMOS technology is not well-suited for this purpose. Scaling PIMs also presents challenges, requiring control of small magnetic moments and often large circuits to convert digital signals into analog voltages, along with other supporting components.

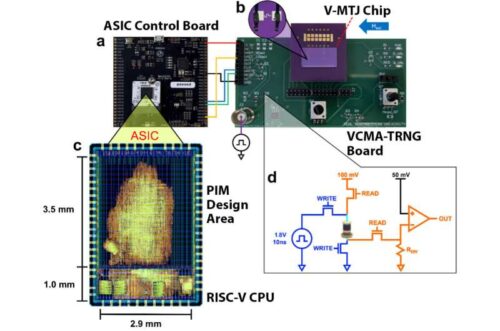

To overcome these limitations, researchers at Northwestern University and other institutes adapted voltage-controlled magnetic tunnel junctions (V-MTJs), originally developed for MRAM, as sources of randomness. The resulting probabilistic computer consists of an array of bistable p-bits implemented with digital CMOS circuitry on an application-specific integrated circuit (ASIC). These p-bits draw random sequences from an adjacent V-MTJ chip and interact to form a probabilistic Ising machine whose energy minimum corresponds to the solution of the computational problem.

In this architecture, two points stand out. First, the system operates digitally and synchronously, with a clock defining intervals for p-bit updates, eliminating the need for large supporting circuits such as digital-to-analog converters. Second, V-MTJs, currently on a separate chip but potentially integrable with the ASIC, save area while delivering random bit sequences and show robustness against device-to-device variations. The approach is compatible with standard CMOS manufacturing and digital design practices, making it promising for fabrication of PIMs capable of solving real-world optimization problems.

The probabilistic architecture was demonstrated to perform integer factorization, a computational problem with a single correct solution that is easy to verify. Beyond factorization, this design can address a range of optimization problems. Future developments aim to integrate V-MTJs directly with CMOS on advanced foundry nodes and expand the system’s applications, creating more compact and capable probabilistic computers.