Designed for EV, aerospace, and energy test systems, the compact boards combine safety interlocks, calibration support, and four-channel density to validate inverters, BMS, and other next-gen power electronics.

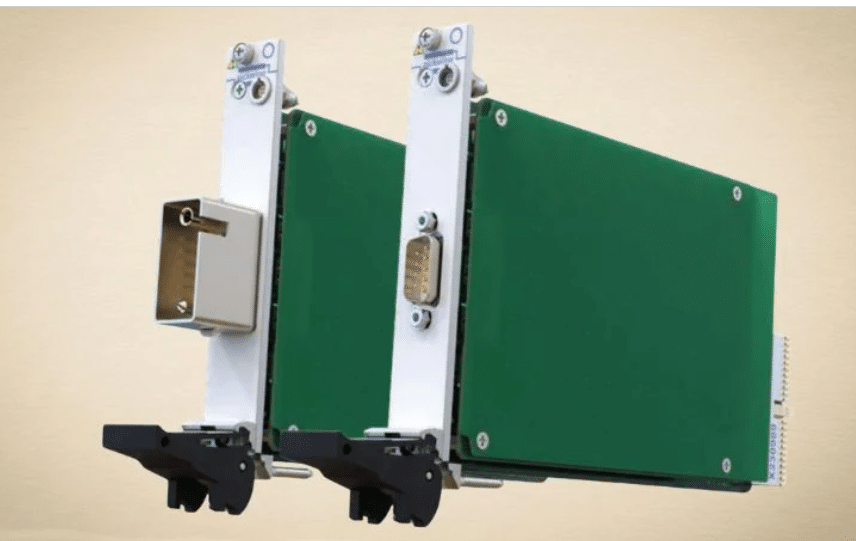

Pickering Interfaces has launched a new family of 1.2 kV PXI and PXIe programmable resistor modules designed to meet the rising demand for high-voltage simulation in electric vehicles, aerospace, and energy systems. The 40-230 (PXI) and 42-230 (PXIe) boards provide compact, single-slot solutions that combine four-channel density, wide resistance ranges, and robust safety features. The key features are:

- Single-slot PXI design saves chassis space

- Provides four-channel high-voltage resistance simulation

- Software allows precise resistor value calls with feedback

- Ensures traceability across automated test sequences

- Supports validation of 1 kV+ architectures

- Speeds safe testing for EV, aerospace, and industrial power systems

With EV platforms moving to 800 V+ battery architectures and aerospace designs shifting to more-electric systems, the need for advanced high-voltage validation tools has become urgent. Pickering’s new modules allow engineers to safely simulate resistive loads, replicate sensor behavior, and insert fault conditions when testing inverters, battery management systems (BMS), and other high-voltage devices.

Flexible High-Voltage Simulation

Each channel can mimic the resistance of RTDs, thermistors, or other sensors, enabling hardware-in-the-loop testing without physical sensor hardware. The boards also support fault insertion—open or short states that verify whether a device under test responds correctly to conditions required by safety standards such as ISO 6469 (EV safety) and IEC 60664 (insulation coordination). The modules further enable voltage isolation testing, ensuring that insulation barriers in BMS and inverter systems meet stringent regulatory requirements—critical for automotive and aerospace safety compliance.

Recognizing the hazards of 1.2 kV environments, Pickering built in a hardware interlock system that forces all relays to their default unpowered state during faults. This interlock can be daisy-chained across multiple modules for coordinated shutdowns, providing a hardware safety layer independent of host PC status. To streamline calibration, engineers can use an optional cable assembly that bypasses the DUT, allowing direct verification of resistor values with a DMM. This reduces downtime and maintains long-term accuracy in automated test systems.