Verification engineers tackling complex SoCs and FPGA designs can now simulate, debug, and optimize with greater speed and confidence, discover how its high-performance engines, broad language support, domain-specific apps, and deep debug capabilities help you catch bugs early and accelerate your verification flow from block to full-chip.

In the fast-paced world of digital hardware design and verification, simulation tools are the backbone of a robust design process. At the forefront of logic simulation is Cadence Xcelium Logic Simulator, a state-of-the-art Electronic Design Automation (EDA) tool used by engineers worldwide to verify complex System-on-Chip (SoC), IP, and digital logic designs before they ever hit silicon. Simply put, Xcelium is a high-performance, scalable simulator that lets engineers exhaustively test and debug hardware designs early in the development cycle, dramatically reducing time-to-market and design risk.

It serves as a core verification engine in modern semiconductor verification flows taking system descriptions written in hardware description languages (HDLs) such as SystemVerilog, Verilog, VHDL, SystemC, and UVM-based testbenches and simulating their behavior in a controlled environment. Through simulation, engineers uncover logic errors, functional mismatches, timing issues, and other bugs long before tape-out, thereby saving substantial development cost and effort.

Key Features That Makes It Design-Engineer’s Favorite

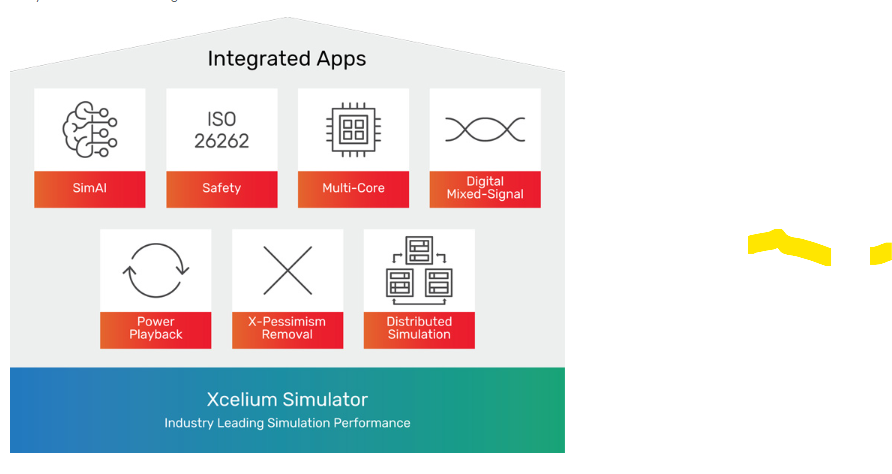

Cadence Xcelium is a feature-rich logic simulation platform designed to help verification engineers simulate, debug, and optimize complex IC designs with high efficiency.

The key features include:

- High-Performance Simulation

- Broad Language & Standards Support

- SimAI

- Multi-Core App

- Safety App

- PowerPlayback

- Distributed Simulation

- Advanced Debug & Waveform Analysis

- Verisium Debug Integration

- Unified Cadence Verification Ecosystem

It delivers high-performance simulation by leveraging parallel and incremental build engines that take full advantage of multi-core hardware, enabling significantly faster regressions on large designs. Xcelium supports a wide range of design and verification languages and industry standards, making it suitable for mixed-language and mixed-signal environments. Its domain-specific Xcelium Apps allow teams to tailor verification for areas such as AI-driven regression acceleration, functional safety, power analysis, and distributed simulation. Advanced debug and verification capabilities provide deep visibility into design behavior through powerful waveform analysis, assertion checks, and coverage metrics, while tight integration with the broader Cadence verification ecosystem ensures a seamless flow from block-level simulation to full-chip verification. As many users note, the debugging and waveform capabilities are indispensable, making signal tracing and driver analysis far more intuitive and efficient.

What’s New in the Latest Xcelium Version

Cadence Xcelium 25.09 is among the latest releases, with documentation updates extending into December 2025. This version reflects Cadence’s ongoing focus on improving simulator performance, scalability, and verification efficiency, especially for today’s large and complex SoC designs. A key theme of the recent updates is the use of distributed processing and intelligent optimization to reduce simulation time while maintaining high accuracy across digital and mixed-signal environments.

Main Features

- Distributed multi-machine simulation

- Improved mixed-signal runtime control

- Faster multi-die and chiplet verification

- Higher scalability and regression performance

One of the most significant enhancements in Xcelium 25.09 is distributed multi-machine simulation, which allows simulation workloads to be partitioned across multiple systems and CPU cores. This significantly improves scalability and makes the tool well-suited for large transistor-level and mixed-signal designs that were earlier limited by single-machine performance.“Fastest HDL simulator I’ve used consistently outperforms other tools in regression runs and helps catch bugs early”, mentioned one engineer.

Another important update is expanded mixed-signal control. The latest version introduces new system tasks that let engineers dynamically adjust analog solver parameters during runtime. This gives verification teams greater flexibility to fine-tune simulation behavior without restarting runs, improving productivity and accuracy in AMS verification flows.“Sometimes slow over remote connections and lacks compact waveform dumps compared to some competitors, but overall a very dependable tool for SoC verification, said an electronics engineer.

Xcelium 25.09 also delivers enhanced multi-die and chiplet simulation performance. With improvements in the Distributed Simulation App, the simulator can achieve up to 3× faster runtimes for complex multi-die designs, enabling more efficient verification of next-generation architectures used in advanced packaging and heterogeneous integration.

Overall, these updates highlight a clear direction for Xcelium: enabling engineers to verify larger, more complex designs faster and more reliably, with better coverage and efficiency than previous versions.

Is There a Free Version? Licensing & Access

Unlike some open-source simulation tools, Xcelium is primarily a licensed commercial product widely used in industry and academia but not freely downloadable for unlimited use by individuals.However:

• Academic Licenses: Universities and research institutions often provide access under educational agreements.

• Verilog Practice Tools: Platforms like EDA Playground let students practice HDL coding and basic simulation with industry syntax without installing Xcelium locally.

• Free Trials: Cadence sometimes offers limited trial access for evaluation or training purposes through its support portal.

There’s no fully free, full-feature version of Xcelium for general use; paid licensing is required for professional verification projects. For engineers serious about designing complex digital systems, Cadence Xcelium is a mission-critical EDA simulator. It combines performance, versatility, advanced debug tools, multi-language support, and an ecosystem that spans formal, emulation, and planning tools making it a cornerstone of modern verification flows. Its ability to harness multi-core and distributed computing, leverage machine learning-based regression optimization, and integrate seamlessly with other Cadence products means design teams can confidently push more thorough verification earlier in the design cycle, reducing costly silicon errors and accelerating time-to-market.

For more information, click here.