One chip brings wireless, wired internet, AI, and security together, so devices can do more work while keeping design simple and easy to build.

Espressif Systems is preparing to launch the ESP32-S31, a dual-core SoC designed for advanced IoT devices. It combines Wi-Fi 6, Bluetooth 5.4, IEEE 802.15.4, and Ethernet, along with support for edge AI, HMI features, and hardware-based security.

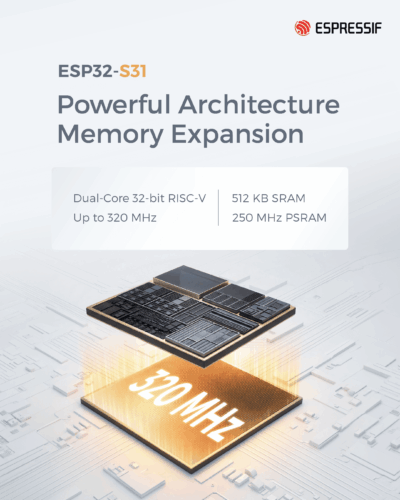

The chip is built around a dual-core, 32-bit RISC-V processor running at 320 MHz. One core includes a 128-bit SIMD data path for parallel workloads. It has 512 KB SRAM and supports up to 250 MHz DDR PSRAM, with simultaneous access to flash and external memory. Multiple SPI options, including Octal SPI, enable flexible memory expansion for data-heavy tasks.

Connectivity is integrated across standards. The ESP32-S31 supports Wi-Fi 6 in the 2.4 GHz band, Bluetooth 5.4 with LE and Classic modes, and IEEE 802.15.4 for Thread and Zigbee. It also supports Matter over both Wi-Fi and Thread. Wi-Fi 6 improves efficiency and power use, while Bluetooth 5.4 adds LE Audio, direction finding, and Mesh networking. A 1000 Mbps Ethernet MAC provides wired connectivity.

For interface design, the chip supports cameras, displays, and touch input. It includes a DVP camera interface (8–16 bit), LCD support (8–24 bit parallel) with hardware color conversion, and up to 14 capacitive touch channels. A JPEG codec, 2D graphics acceleration, and 2D-DMA handle image and display processing.

Audio support includes Bluetooth LE Audio and Classic audio. Dual I2S controllers with hardware-level synchronization help maintain low latency without software overhead.

Security features include RAM-based PUF for key management, secure boot, flash and PSRAM encryption, a digital signature block, and cryptographic acceleration. The chip also includes protection against side-channel and power glitch attacks, along with a Trusted Execution Environment for application isolation.

It also integrates USB OTG, TWAI (CAN 2.0 compatible), Ethernet MAC, and standard interfaces such as I2C, I2S, SPI, UART, PWM, ADC, SDIO, timers, and DMA.

Click here for the original announcement.