Making custom chips takes time and costs money. This tool makes it fast, lowers cost, and makes it simple, so devices can be built quicker.

Designing custom chips is slow, costly, and prone to errors. For companies building embedded systems, IoT devices, or edge AI solutions, developing a System-on-Chip (SoC) from scratch can take months of engineering effort. This delays time-to-market, increases costs, and makes it harder to keep up with fast-changing product needs.

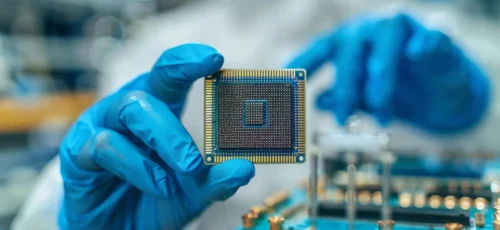

InCore Semiconductors addresses this challenge with its SoC Generator Platform. Instead of spending months designing frontend chip architecture, engineers can now generate a full SoC in just a few minutes. The platform automates complex tasks like integrating processor cores, peripherals, interconnects, and software stacks, cutting development time dramatically while reducing design risks and cost.

A test chip built using the platform shows how it works in practice. It includes six different RISC-V processor cores, a custom Network-on-Chip (NoC) that handles automatic protocol bridging, various peripherals, and a complete Real-Time Operating System (RTOS). This proves the system is ready for real-world applications.

The solution is especially useful for embedded system developers, IoT startups, and companies working in networking or edge AI who need fast, flexible, and low-cost chip designs. The platform offers three processor families for different needs:

- Azurite is made for ultra-low power applications like motor control and battery-powered devices, where fast interrupt response and precise timing are critical.

- Calcite suits mid-tier embedded products such as POS terminals and smart cameras, offering a balance of performance and energy efficiency.

- Dolomite (coming soon) will target advanced use cases requiring high-performance vector processing and virtualization, helping developers manage complex workloads in networking and AI.

With this platform, hardware developers can focus on building features and solving real application problems, rather than getting bogged down in long, costly chip design cycles.