Featuring integrated AI acceleration, advanced error correction, and near-threshold operation, it delivers unmatched energy efficiency for always-on devices—from wearables and drones to smart IoT systems—ushering in a new era of intelligent, battery-optimized design.

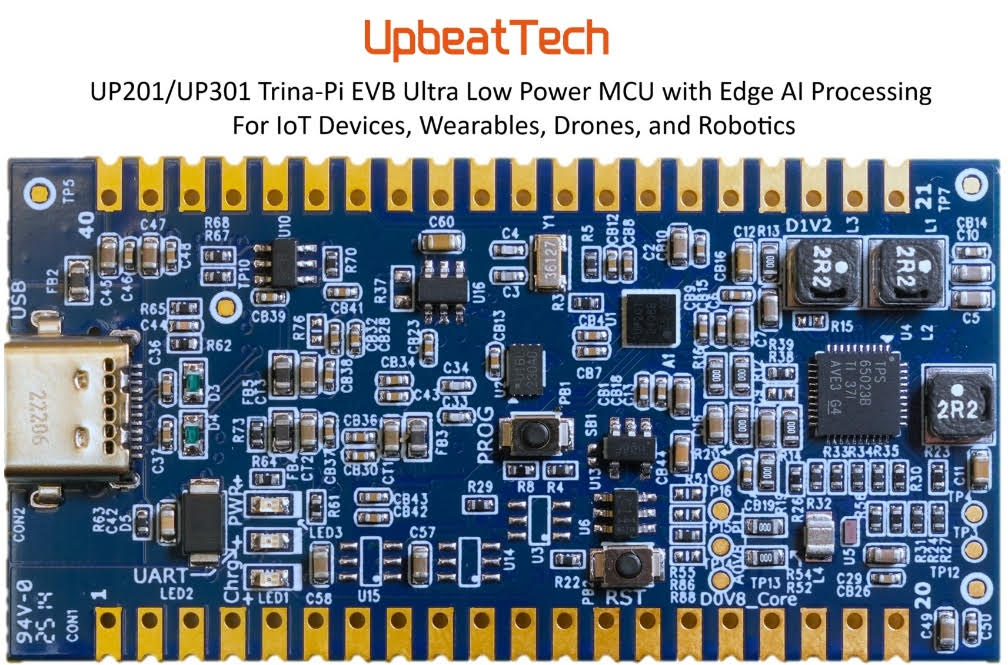

Upbeat Technology and SiFive have teamed up to unveil the UP201/UP301 MCU family—a dual-core RISC-V microcontroller platform designed to push the limits of low-power intelligence at the edge. The chips blend SiFive’s Essential IP cores with Upbeat’s proprietary AI acceleration and power management technologies, aiming squarely at the next wave of battery-powered devices.

At the core of the new MCU family lies a heterogeneous dual-core RISC-V architecture paired with dual AI accelerators that promise a step-change in power-to-performance efficiency. Built for always-on IoT, wearables, drones, and smart sensing systems, the UP201/UP301 platform delivers an ultra-low energy profile of 16.8 μW/MHz/DMIPS—making it one of the most efficient edge processors in its class. Upbeat’s patented Error Detection and Correction (EDAC) and SRAM optimization further enhance resilience under near-threshold operation.

The key features are:

- Operates up to 400 MHz with 717 DMIPS performance

- Optimized for edge AI workloads including inference, sensor fusion, and DSP-based signal processing

- Delivers high compute power with ultra-low energy use, outperforming typical ARM-based MCUs

- Enables developers to build smarter, battery-efficient AI applications on microcontrollers

In a preview of real-world performance, early adopters like Awan-sensing have reported exceeding power targets while maintaining real-time responsiveness. The integration of AI accelerators and DSP co-processing allows developers to run richer models, extend duty cycles, and improve user experiences—all without draining battery life.

SiFive’s partnership plays a crucial role in this innovation story. By leveraging its Essential Family of RISC-V cores, SiFive helps Upbeat deliver a platform that embodies the open-source hardware ecosystem’s promise: scalable, flexible, and energy-aware design for the intelligent edge.

Live demos at the RISC-V Summit will showcase the MCU alongside Upbeat’s ultra-low-power MEMS Bone Conduction Microphone, with sessions diving into heterogeneous RISC-V edge AI design. Engineering samples, SDKs, and reference resources are already available, setting the stage for a new era of efficient, AI-ready microcontrollers.