A memory device does the unexpected as it gets smaller and performs better, pointing to longer battery life and lower energy use.

Researchers at Institute of Science Tokyo have developed a 25-nanometer memory device that becomes more efficient as it gets smaller, challenging the assumption in chip design that miniaturization reduces efficiency at small scales. In most electronics, shrinking components creates more heat, electrical leakage, and energy loss. In this case, reducing the size improved performance.

The device uses hafnium oxide, a material already used in semiconductor manufacturing. That gives the design an advantage over experimental memory technologies because it could fit into existing production systems instead of requiring new manufacturing processes.

The researchers focused on a problem in nanoscale memory: crystal grain boundaries. At small sizes, these boundaries interrupt electron flow and create energy loss. Instead of changing the fabrication process to work around those defects, the team reduced the size of the device further, lowering the number of grain boundaries inside the structure.

They also used a fabrication process in which heated electrodes formed semicircular shapes, creating a structure closer to a single crystal. That reduced leakage and improved switching. The result was that performance increased as the device size decreased, going against the expectation that smaller devices become less stable and less efficient.

If the technology can be produced at scale, it could affect a range of devices. Smartphones could run longer on one charge, wearable devices could operate longer between charges, and laptops could use less power during heavy workloads. In AI systems and data centers, where memory movement accounts for a growing share of power use, more efficient memory could reduce energy costs.

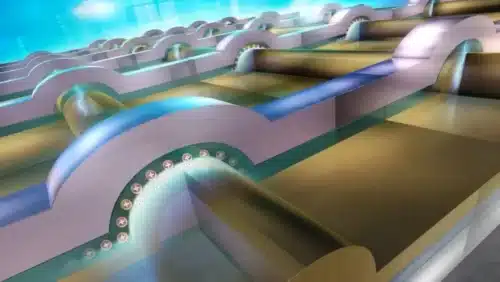

The device is based on a type of memory called a ferroelectric tunnel junction, or FTJ. Unlike conventional memory, which stores data through electrical charge, FTJs store information by switching the electric polarization inside a material between two stable states. That allows data to remain stored without constant power while reducing energy use during operation.

The broader implication is that chip scaling may not have the efficiency limit the industry assumed. For years, semiconductor progress has depended on making components smaller while accepting energy losses as part of the tradeoff. This work suggests that, in some cases, shrinking devices can improve performance instead of reducing it.