For semiconductor designers this outlines how a thin ferroelectric stack can retain polarization and support memory integration.

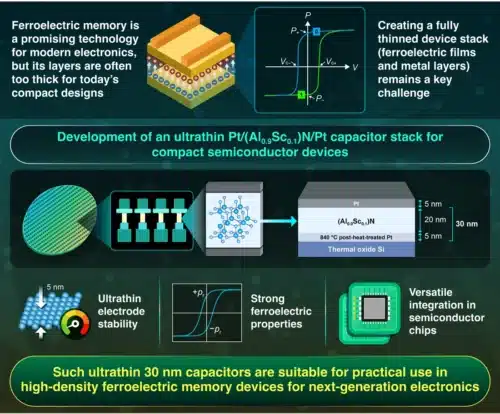

As electronic devices become increasingly compact, there is growing demand for memory materials that can efficiently store data at reduced dimensions. Ferroelectric memory devices, which retain information through switchable electric polarization even without power, are promising candidates for future mobile and compact electronics. However, few studies have demonstrated downscaling of complete ferroelectric devices.

To address this, a research team led by Professor Hiroshi Funakubo at the School of Materials and Chemical Technology, Institute of Science Tokyo, in collaboration with Canon ANELVA Corporation, successfully reduced the total thickness of a ferroelectric memory capacitor stack to just 30 nm, including top and bottom electrodes.

The researchers developed a three-layer capacitor structure using a scandium-substituted aluminum nitride ((Al0.9Sc0.1)N) ferroelectric layer enclosed between platinum electrodes. The optimized stack consists of a 5 nm platinum bottom electrode, a 20 nm (Al0.9Sc0.1)N layer, and a 5 nm platinum top electrode. This configuration maintains strong ferroelectricity, with high remnant polarization and is compatible with direct integration into semiconductors and logic circuits.

Funakubo says, “High ferroelectric performance can be sustained even when the entire capacitor stack thickness is drastically reduced, bringing us closer to practical implementation of ultrathin memory devices.”

The study provides a foundation for compact ferroelectric memories and may inform downscaling of other architectures such as FeRAM and FTJ. Future work will explore alternative electrode materials to improve durability and reduce thermal processing requirements.