With doubled I/O interfaces and refined low voltage TSV design, HBM4 reshapes how memory stacks sustain throughput under data centre scale loads.

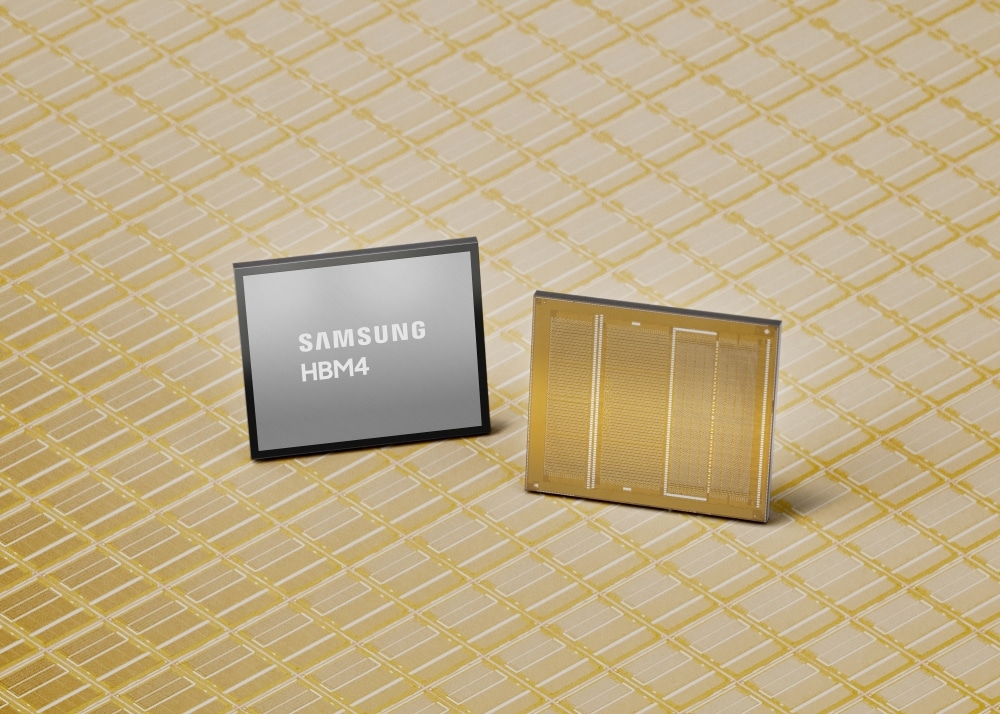

Samsung Electronics has introduced its HBM4 memory and begun mass production, marking what it describes as an industry first for the next-generation high-bandwidth memory standard. The device targets AI computing and data center workloads that demand higher throughput and energy efficiency.

Built using the company’s sixth-generation 10nm-class DRAM process (1c) and a 4nm logic base die, the new memory stack is designed to maximize performance, reliability and power efficiency. The architecture delivers a consistent data transfer speed of 11.7Gbps, with performance scalable up to 13Gbps. This exceeds the 8Gbps industry benchmark by roughly 46% and represents a 1.22x increase over the 9.6Gbps maximum pin speed of HBM3E.

Total bandwidth per stack reaches up to 3.3TB/s, a 2.7x increase compared to its predecessor. Using 12-layer stacking technology, capacities range from 24GB to 36GB, with a future 16-layer configuration planned to extend capacity up to 48GB.

To address the doubling of data I/Os from 1,024 to 2,048 pins, advanced low-power design techniques were integrated into the core die. The memory achieves a 40% improvement in power efficiency through low-voltage through-silicon via (TSV) technology and power distribution network optimization. Thermal resistance improves by 10%, while heat dissipation increases by 30% compared to HBM3E.

A tightly integrated Design Technology Co-Optimization (DTCO) between foundry and memory operations supports yield and quality control, while in-house advanced packaging capabilities help streamline production cycles.

Sang Joon Hwang, Executive Vice President and Head of Memory Development at Samsung, says, “By leveraging our process competitiveness and design optimization, we are able to secure substantial performance headroom, enabling us to satisfy our customers’ escalating demands for higher performance, when they need them.”