Free, fast, and fiercely trusted Verilator keeps digital design honest before hardware ever hits the fab.

Verilator is an open-source compiler that transforms synthesizable Verilog/System Verilog RTL into highly optimized C++ or SystemC models. Instead of interpreting HDL, it “Verilates” the design, compiling it into a fast, cycle-accurate executable using a standard C++ toolchain.

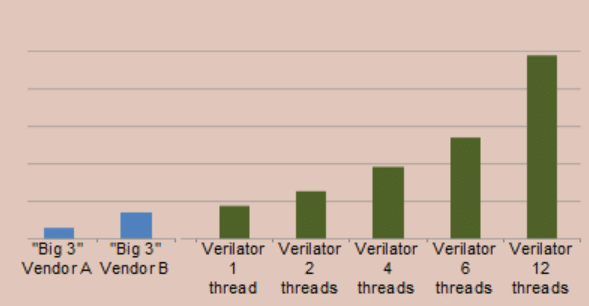

This approach delivers significantly higher performance than traditional event-driven simulators, often achieving 10× the speed of single-threaded SystemC and 100× or more compared to interpreted tools like Icarus Verilog. With multithreading, speed-ups can reach 200–1000×.

Beyond simulation, Verilator provides linting, code-quality checks, coverage generation, and efficient parallel execution for large projects. In practice, it often matches or exceeds the performance of commercial simulators. And because it’s fully open source, you scale using compute not licenses giving exceptional simulation throughput per dollar.

These capabilities make it especially valuable when dealing with complex ASIC or SoC-scale designs that demand higher performance than interpreter-based simulators can offer. Its C++/SystemC integration enables sophisticated verification environments where software and hardware models run together, improving co-simulation accuracy.

And because Verilator is completely open source, teams are not limited by license counts, simulation capacity scales purely with available compute resources, allowing many parallel regressions without cost barriers.

Fast

In practice, it provides digital designers with a fast, efficient “pre-hardware” verification flow, much like how analogue engineers rely on LTspice before building real circuits. It encourages early simulation, rapid iteration, and bug-fixing long before hardware or silicon prototypes exist.

Given how time-consuming and expensive late-stage RTL bugs can be, Verilator helps engineers shorten the design cycle and improve confidence in their RTL through faster regressions, stronger code checks, and smoother early integration.

The main features that make Verilator attractive:

- Converts synthesizable Verilog/parts of System Verilog into C++ or SystemC simulation models.

- Very high simulation performance (thanks to compilation into optimized C++ and optionally multithreaded execution) outperforming many interpreted simulators.

- Support for linting/code-quality checking on HDL input (warns/errors) as part of the flow.

- Integration with C++/SystemC environments i.e.,can wrap the generated model and build sophisticated verification/testbench flows.

- Support for multithreading (to exploit modern multi-core machines) in simulation.

- Good adoption in open-source/academic/industrial flows;robust community and many contributors.

- Free/open-source licensing (LGPL-3.0 or Artistic License)meaning no upfront license cost barriers.

- Cross-platform (Linux, Windows via WSL/Cygwin) with documentation covering installation and usage.

Together, these features make Verilator a compelling “first stop” for digital verification engineers: you can run your RTL, iterate quickly, and validate behavior before moving to slower/fuller(perhaps commercial) simulators or emulation/hardware.

What’s new?

The latest version of Verilator is 5.042 (released November 2025).In the earlier 2025-02 release (Version 5.034), Verilator added several important upgrades aimed at strengthening SystemVerilog verification.

The update introduced expression coverage, allowing engineers to measure coverage at a finer level than simple statements.

It also improved VPI functionality with support for multidimensional array access, a useful addition for advanced verification environments. Some of the new enhancements in recent updates include:

- Hierarchical parameter checks: New HIERPARAM error flags incorrect parameter values in hierarchical designs.

- Array dimension validation: Errors now raised for zero or negative unpacked dimensions.

- DPI import profiling: verilator_gantt adds performance profiling for DPI imports.

- ASAN build option: New enable-dev-asan flag enables Address Sanitizer builds for catching memory bugs.

- Thread-pool improvements: Default thread-pool sizes now respect CPU affinity for better parallel performance.

- Modport/clocking support: Enhanced SystemVerilog handling for modports referencing clocking blocks.

Beyond this, the release expanded SystemVerilog feature support by enabling nested classes and enhancing constrained-random capabilities, including randomisation for arrays inside structs bringing Verilator closer to mainstream verification workflows.

Why Verilator Excels and Where It Still Falls Short?

From a verification engineer’s viewpoint, the recent enhancements in Verilator are particularly exciting because they strengthen both coverage quality and simulation efficiency.

The addition of expression-level coverage enables far more detailed measurement of what the testbench actually exercises, improving verification confidence. Updates to thread-pool handling and processor-affinity make it easier to exploit multi-core systems, a major advantage when running large regressions.

New profiling tools for DPI imports and ASAN integration signal that Verilator is maturing into a more robust, developer-friendly platform.

Combined with stronger SystemVerilog support covering classes, constraints and structured arrays, these improvements significantly narrow the gap between open-source and commercial verification flows, making Verilator increasingly attractive for large SoC and open-hardware projects where speed, scalability and cost freedom are critical.

Engineers often describe Verilator with a mix of admiration and caution. As one user puts it, “My main issues with Verilator are fourfold, Verilator has no format for encrypted IP, it doesn’t allow # statements, it cannot handle mixed Verilog and VHDL, and it is two-state, not four-state.” This highlights important practical limitations: teams relying on vendor-encrypted IP, VHDL blocks, four-state logic (X/Z), or behavioural delay modelling may find gaps in what Verilator can support.

By contrast, another designer underscores what makes the tool so compelling: “A single computer can simulate an SoC design at reasonable speed, Verilator is amazing for building huge systems, it’s totally free, so the number of simulations you run in parallel is bounded by compute availability rather than licenses.” Here, the message is clear: its speed and zero-license model give teams the freedom to scale regressions massively, making it especially attractive for open-source, research, and startup environments. Yet the community tempers the praise with a note of realism.

As one of the users added comments, “I know of people who swear by Verilator, while such an opinion certainly can be useful, I’d be cautious.” This caution reflects the recurring theme: Verilator excels at what it targets, but it isn’t a drop-in replacement for every verification flow.

- Pros: Very fast SoC-scale simulation, scales easily on a single machine, and offers unlimited parallel regressions thanks to zero licensing cost.

- Cons: Lacks support for encrypted IP, mixed Verilog/VHDL designs, four-state logic (X/Z), and behavioral delay modelling limiting use in some commercial flows.

Overall, these perspectives converge on a balanced view: Verilator delivers exceptional performance, openness, and cost advantages, but users must remain aware of trade-offs in language support, verification methodology, four-state accuracy, mixed-language capability, and handling of encrypted IPan important nuance for any EDA-focused audience.

Free version/licensing/capabilities

- Free & Open Source: Licensed under LGPL v3.0 or Artistic v2.0; no per-seat or per-core costs.

- Unlimited Parallel Sims: Runs limited only by available compute, not licenses.

- No Paid “Pro” Version: Core tool is fully free; only optional commercial support exists.

- Rich Free Features: RTL-to-C++ conversion, fast simulation, expression coverage, multithreading, linting, waveforms, C++/SystemC integration.

- Key Limitations: No encrypted IP format, no full four-state/event-driven support, limited mixed-language/VHDL, gaps in UVM and AMS flows.

- Best For: Teams using synthesizable Verilog/SystemVerilog RTL.

- May Need Extras: If workflows involve VHDL, encrypted IP, analog/mixed-signal, or strict four-state modelling.

Limitations to note:

- Encrypted/vendor IP may not be supported

- Mixed-language designs (VHDL + Verilog) not handled natively

- No full four-state logic (X/Z) modelling

- Legacy # delay constructs not supported

Verilator may not cover every corner case of commercial simulators, but teams continue to rely on it because it delivers where it matters most: fast RTL simulation, early-stage verification, and massive regression scalability without license barriers. Its open-source nature makes it easy to deploy across large compute farms, turning parallelism into straightforward productivity gains.

For many ASIC and FPGA groups, Verilator has become the trusted “first stop before hardware” simple to adopt, efficient to run, and backed by an active community. Even if it lacks some advanced vendor-specific features, it remains a powerful, reliable, and cost-free tool that fits perfectly into modern verification workflows.

Download and install Verilator.

Smart Practices For New Verilog UsersStart Small: Begin with simple modules before larger designs.Keep Code Clean: Use clear naming, indentation, and structure. Simulate Often: Catch issues early with frequent test runs. Always Use a Testbench: Even a basic one prevents regressions. Use Non-Blocking assignments (<=) for Sequential Logic: Avoid race conditions. Modularise: Break designs into smaller, reusable blocks. Learn Basic SystemVerilog: logic, always_ff, always_comb improve reliability. Use Version Control: Track changes and experiment safely. Read Waveforms Well: Get comfortable with GTKWave or similar tools. Check with Linters: Use Verilator lint or Verible to spot mistakes. Know Synthesizable Constructs: Understand what maps to hardware. Document Briefly: Note assumptions, interfaces, and decisions. |