Researchers at Pohang University of Science and Technology have developed an AI‑driven method that could transform how analog semiconductor layouts the physical blueprints of circuits are created, potentially cutting design effort and speeding production in electronics.

Designing analog circuit layouts is notoriously challenging and manual. Unlike digital circuits, analog layouts require careful placement and routing of components to meet strict performance, reliability and manufacturing rules, a process that has long depended on expert engineers and resisted automation. Data scarcity adds another hurdle: detailed layout data is often proprietary and unavailable for training machine learning systems.

Addressing these challenges, a team at the Pohang University of Science and Technology (POSTECH) in South Korea applied a foundation model approach, a technique where a large model is pre‑trained on broad datasets and then fine‑tuned for specific tasks to analog layout design.

The researchers used self‑supervised learning, a method where the AI learns patterns without labeled examples, by splitting real layout designs into patches, masking parts, and training the model to reconstruct the missing elements. This strategy generated around 320,000 training samples from six real datasets, enabling the model to learn recurring structural patterns in analog layouts.

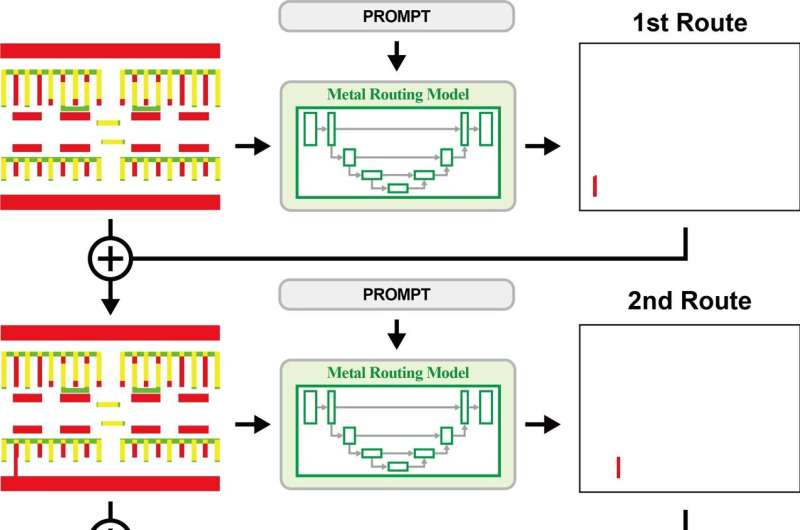

Once pre‑trained, the foundation model was adapted to five distinct layout tasks, including generating contacts and vias (connections between layers), inserting dummy patterns to improve manufacturing yield, shaping regions like N‑wells, and metal routing. In tests, layouts produced by the AI passed 96.6 % of design‑rule checks and schematic verification tests. Moreover, the model achieved similar performance using only about one‑eighth the data typically required by traditional methods.

Instead of crafting separate AI tools for each layout task, this approach suggests a single adaptable model could handle multiple layout challenges, reducing both development time and engineering workload in chip design. POSTECH researchers say this could significantly improve productivity in analog design workflows and help tackle one of the industry’s stubborn automation bottlenecks. While practical adoption and integration into commercial electronic design automation (EDA) tools remain future steps, the research marks a meaningful advance toward scalable, AI‑assisted analog layout designs traditionally bespoke and labor‑intensive craft.