New desktop processor doubles down on 3D cache to deliver gains in latency, throughput, and creative workloads.

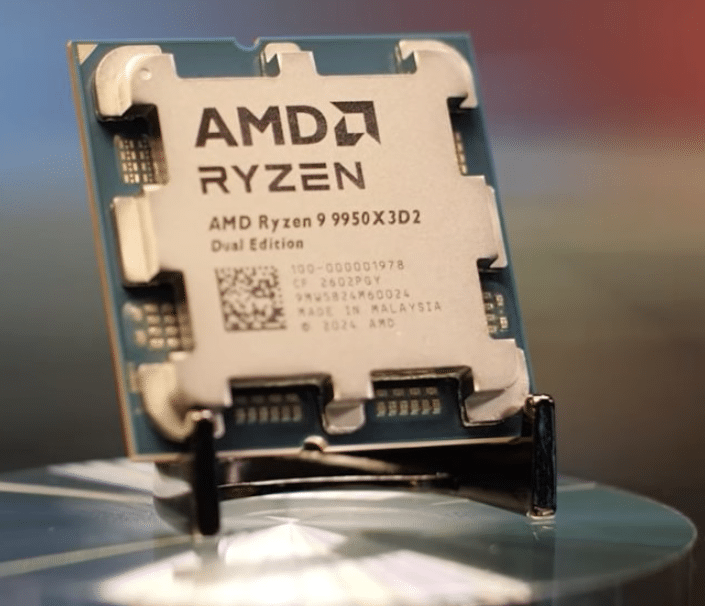

A new high-end desktop processor by AMD featuring dual-stacked cache architecture is set to hit global markets on April 22, marking a significant step forward in CPU design for performance-intensive applications. The chip introduces a first-of-its-kind approach in the desktop segment by integrating 3D-stacked cache across both compute chiplets, targeting improved latency and data throughput for demanding workloads.

The key features are:

- Dual chiplet design with 3D-stacked cache on both dies

- 16-core architecture based on next-gen CPU design

- 208MB total cache for reduced latency

- 5–10% performance uplift in creative and dev workloads

- Optimized for rendering, video processing, and code compilation

Built on a next-generation core architecture, the processor packs 16 cores and an unprecedented 208MB of total cache, the highest ever in its class. By extending 3D V-Cache technology to both chiplets instead of a single die, the design aims to eliminate bottlenecks typically associated with cache access imbalance in multi-chiplet processors. This results in faster data availability to cores, which is critical for applications such as video rendering, 3D modeling, and large-scale code compilation.

Early performance projections indicate gains of 5–10% over its predecessor in creative and developer-focused workloads. These include tools like Blackmagic’s DaVinci Resolve for video processing, Blender for 3D rendering, and large codebases such as Unreal Engine and Chromium builds. The improvements stem largely from reduced memory latency and increased cache bandwidth, rather than raw clock speed enhancements.

The launch reflects a broader industry trend toward cache-centric CPU innovation, where increasing on-chip memory is becoming as crucial as adding cores. This approach is particularly relevant as workloads grow more data-intensive and demand faster access to frequently used datasets.

With dual 3D-stacked cache now implemented at scale in desktop processors, the architecture could set a new benchmark for high-performance computing tasks, especially in creator and developer ecosystems.